Register-Transfer Level (RTL)

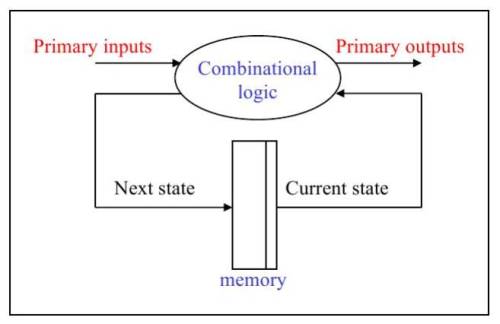

At the register-transfer level, the timing of a design is specified at the resolution of clock cycles: one knows what has to happen from the moment that a register output value changes until new values become available to update the registers in the next clock cycle. If one sees a design as a state machine in which the registers hold the system state, hardware at the RT level obeys the model of the figure below. The figure depicts a so-called Mealy-type finite state machine. Combinational logic computes the next state and outputs from the current state and current inputs.